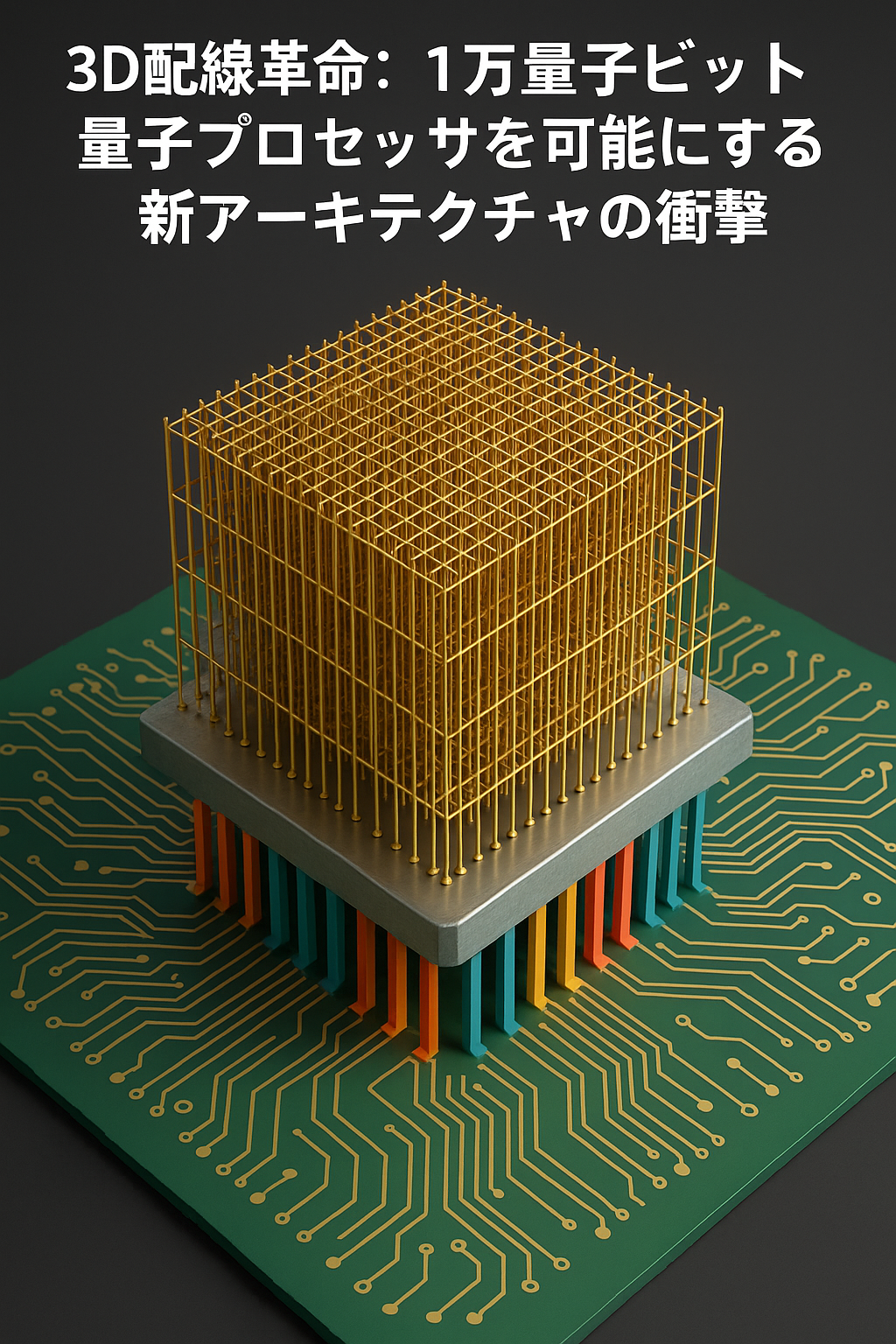

3D配線革命:1万量子ビット量子プロセッサを可能にする新アーキテクチャの衝撃

2025年12月、量子ハードウェア分野に決定的なブレークスルーが報告された。

オランダの量子企業 QuantWare が開発した新しい3D配線アーキテクチャにより、

1万量子ビット(10,000 qubits)を単一チップで実現可能になったという。

しかもそのチップサイズは、

現在の100量子ビット級プロセッサよりも小さい。

なぜ従来の量子チップはスケールしなかったのか?

現在の量子プロセッサ(QPU)は、古典CPUと同様に、

- 2次元(水平)配線

- ウェハー上に配線を敷き詰める構造

を採用している。

この方式では、

- 配線本数に物理的限界がある

- 量子ビットを増やすほどノイズと干渉が増える

という問題が避けられない。

実際、

- Google:約105量子ビット

- IBM:約120量子ビット

が、現行世代の上限だった。

解決策:VIO-40K「垂直3D配線アーキテクチャ」

QuantWareが発表した新技術は、

VIO-40K(Vertical I/O 40K) と呼ばれる。

主な特徴

- 3次元(垂直)配線を採用

- 40,000本のI/Oラインをサポート

- 「超高忠実度(Ultra-high-fidelity)」な

チップ間接続技術 - チップレット(chiplet)構造

これにより、

単一QPUで1万量子ビットを同時に扱える

という、従来比100倍のスケールアップを実現した。

チップレット技術が生む「量子SoC」

従来の量子拡張では、

- 複数チップを接続

- チップ間通信の精度が低下

- そこが性能ボトルネック

という問題があった。

VIO-40Kでは、

- 小型モジュール(チップレット)を個別製造

- 高忠実度で密封・統合

- 単一の量子SoC(System-on-a-Chip)として動作

これにより、

- チップ間通信劣化を回避

- 実質「1枚の巨大量子チップ」として機能

する。

産業的インパクト:量子は「理論」から「経済価値」へ

QuantWare CEO Matt Rijlaarsdam は次のように語る。

「業界は長年、100量子ビットで足踏みし、

実用的な量子技術は“遠い未来”として語られてきた。

VIOはそのスケーリングの壁を取り払う」

これはつまり、

- 量子化学

- 材料設計

- エネルギー

- 金融最適化

といった分野で、

“経済的に意味のある量子計算”が現実化する可能性を示す。

IBMロードマップとの決定的な違い

参考として、

- IBMの公式ロードマップ

→ 2,000量子ビット:2033年以降

→ 10,000量子ビット:未定

一方でQuantWareは、

- 2026年:デルフトに量子専用ファブ稼働

- 2028年:VIO-40K出荷開始予定

👉

5年以上の時間差が生まれる可能性がある。

オープン戦略(QOA)が武器になる

QuantWareの大きな特徴は、

エンドツーエンド型ではないこと。

- Google / IBM:

ハード・ソフト・スタックを自社完結 - QuantWare:

量子オープンアーキテクチャ(QOA)

連携可能なエコシステム

- Qblox:量子制御

- Nvidia:ソフトウェア

- NVQLINK:QPUとGPUの接続

- CUDA:既存HPC・AI開発環境

これにより、

- 量子+GPUのハイブリッド計算

- 既存スーパーコンピュータとの統合

- 量子VM的な使い方

が容易になる。

「量子版Intel」になる可能性

この立ち位置は、

- 自社で全てを囲い込まない

- インフラレイヤーを提供

- 他社と組んでエコシステムを拡大

という点で、

IntelがPC産業で果たした役割に近い。

👉

QuantWareは将来、

量子コンピューティングの基盤ハードウェア企業になる可能性がある。

まとめ|量子スケーリング問題は、ついに突破されたか?

- 2D配線 → 3D垂直配線

- 数百量子ビット → 1万量子ビット

- 研究用途 → 経済価値のある量子計算

VIO-40Kは、

量子コンピューティングを「理論上すごい技術」から

「実装可能な産業インフラ」へ引き上げる転換点になり得る。

量子の本当の時代は、

エラー訂正だけでなく“配線”から始まったのかもしれない。